# **4096-Stage Low Voltage Operation Low Noise BBD**

V3205SD

#### General description

The V3205SD is a 4096-stage low voltage operation (VDD = 5V) BBD that provides a signal delay of up to 204.8ms at clock frequency 10KHz and is suitable for use as reverberation effect of audio equipments such as portable stereo and radio cassette recorders which need low voltage and long delay time since S/N is 60dB in spite of many stages.

#### Features

- Variable delay of audio signals: 20.48ms ~ 204.8ms.

- Wide power supply voltage: 4 ~ 8V.

- No insertion noise: Li = 0dB typ.

- Wide dynamic range: S/N = 60dB.

- N Channel silicon gate process.

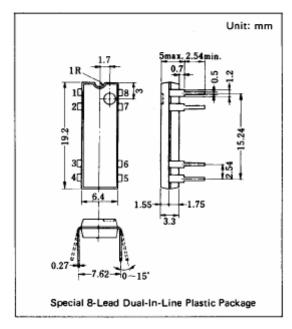

- Special 8-Lead Dual-In-Line plastic Package.

#### Applications

- Reverberation and echo effects of audio equipment such as radio cassette recorder, car radio, portable radio, portable stereo, echo microphone and pre-taped musical accompaniment (Karaoke), etc.

- Sound effect of electronic musical instrument.

- Variable or fixed delay of analog signals.

- Telephone time compression and delay line for voice communication system.

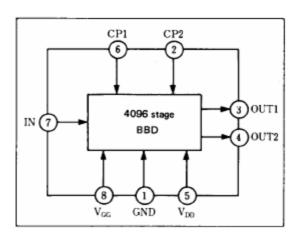

#### Block Diagram

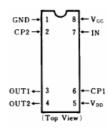

## ■ Pin Configuration

| No. | Symbol   | Туре | Description                       |

|-----|----------|------|-----------------------------------|

| 1   | GND      | Р    | Ground                            |

| 2   | CP2      | I    | The second clock input            |

| 3   | OUT1     | 0    | Signal output, delayed 4096 times |

| 4   | OUT2     | 0    | Signal output, delayed 4097 times |

| 5   | $V_{DD}$ | Р    | Power                             |

| 6   | CP1      | I    | The first clock input             |

| 7   | IN       | I    | Analog signal input               |

| 8   | $V_{GG}$ | I    | Bias voltage input (14/15VDD)     |

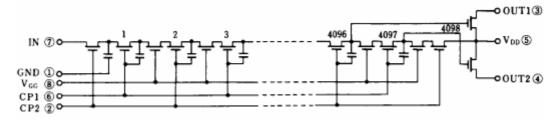

# ■ Circuit Diagram

## ■ Quick Reference Data

| Item                      | Symbol              | Value                      | Unit |

|---------------------------|---------------------|----------------------------|------|

| Supply Voltage            | $V_{DD}$ , $V_{GG}$ | $+5$ , $^{14}/_{15}V_{DD}$ | V    |

| Signal Delay Time         | t <sub>D</sub>      | 20.48 ~ 204.8              | ms   |

| Total Harmonic Distortion | THD                 | 0.8                        | %    |

| Signal to Noise Ratio     | S/N                 | 60                         | dB   |

# ■ Absolute Maximum Ratings (Ta = 25°C)

| Item                    | Symbol                                   | Rating     | Unit                   |  |

|-------------------------|------------------------------------------|------------|------------------------|--|

| Terminal Voltage        | $V_{DD}$ , $V_{GG}$ , $V_{CP}$ , $V_{i}$ | -0.3 ~ +11 | V                      |  |

| Output Voltage          | Vo                                       | -0.3 ~ +11 | V                      |  |

| Operation Ambient Temp. | T <sub>opr</sub>                         | -20 ~ +60  | $^{\circ}$             |  |

| Storage Temp.           | T <sub>stq</sub>                         | -55 ~ +125 | $^{\circ}\!\mathbb{C}$ |  |

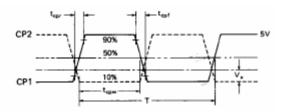

## Operating Condition (Ta = 25°C)

| Item                  | Symbol           | Condition | Min. | Тур.                | Max                | Unit |

|-----------------------|------------------|-----------|------|---------------------|--------------------|------|

| Drain Supply Voltage  | $V_{DD}$         |           | +4   | +5                  | +8                 | V    |

| Gate Supply Voltage   | $V_{GG}$         |           |      | $^{14}/_{15}V_{DD}$ |                    | V    |

| Clock Voltage High    | $V_{CPH}$        |           |      | $V_{DD}$            |                    | V    |

| Clock Voltage Low     | $V_{CPL}$        |           | 0    |                     | +0.5               | V    |

| Clock frequency       | f <sub>CP</sub>  |           | 10   |                     | 100                | kHz  |

| Clock Pulse Width *1  | t <sub>CPW</sub> |           |      |                     | 0.5T <sup>*2</sup> |      |

| Clock Rise Time *1    | t <sub>CPr</sub> |           |      |                     | 500                | ns   |

| Clock fall Time *1    | t <sub>CPf</sub> |           |      |                     | 500                | ns   |

| Clock Input Capatence | C <sub>CP</sub>  |           |      |                     | 2800               | рF   |

| Clock Cross Point     | $V_X$            |           | 0    |                     | $0.3V_{CPH}$       | V    |

#### ■ Electrical Characteristics

(Ta = 25°C,  $V_{DD}$  = VCPH = 5V, VCPL = 0V, VGG = 14/15 VDD, RL=100k $\Omega$ )

| Item                  | Symbol          | Condition                         | Min.  | Тур. | Max.  | Unit       |

|-----------------------|-----------------|-----------------------------------|-------|------|-------|------------|

| Signal Delay time     | t <sub>O</sub>  |                                   | 20.48 |      | 204.8 | ms         |

| Input Signal Freq.    | f <sub>i</sub>  | $f_{CP} = 40kHz$ ,                | 6     |      |       | kHz        |

|                       |                 | Output Attenuation ≤ 3dB          |       |      |       |            |

| Input Signal Swing    | V <sub>i</sub>  | THD = 2.5%                        | 0.36  |      |       | $V_{rms}$  |

| Insertion Loss        | L <sub>i</sub>  | $f_{CP} = 40kHz, f_i = 1kHz$      | -4    | 0    | 4     | dB         |

| Total Harm. Dist.     | THD             | $f_{CP} = 40kHz$ , $f_i = 1kHz$ , |       | 8.0  | 2.5   | %          |

|                       |                 | $V_i = 0.25 V_{rms}$              |       |      |       |            |

| Output Noise Voltage  | V <sub>ON</sub> | $t_{CP} = 100 \text{ kHz},$       |       |      | 0.35  | $mV_{rms}$ |

| Signal to Noise Ratio | S/N             | Weighted by "A" curve             |       | 60   |       | dB         |

<sup>\* 1</sup> Clock Pulse Waveform

$<sup>^{*2}</sup>$  T = 1/f<sub>CP</sub> (Clock Period)

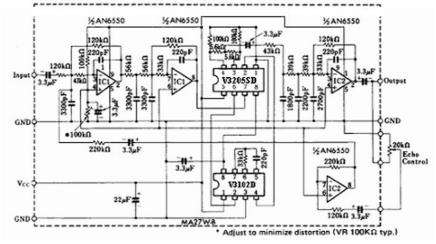

#### Application Circuit

## ■ Mechanical Specification